Verilog 学习使用实验技术报告

...大约 3 分钟

Verilog 学习使用实验技术报告

Verilog 是一个硬件语言,说实话,我真的很不喜欢这门语言。无奈要学,身不由己!

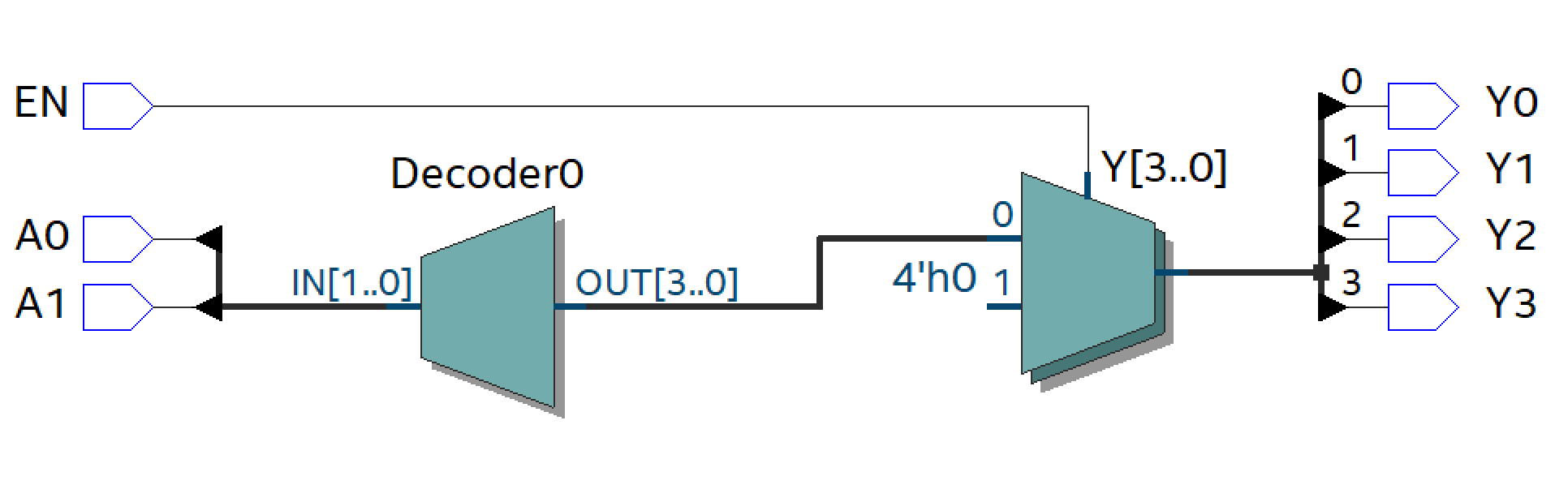

24 译码器

module Vr2to4dec(A0, A1, EN, Y0, Y1, Y2, Y3);

input A0, A1, EN;

output reg Y0, Y1, Y2, Y3;

always @ (A0, A1, EN)

if (EN == 1)

{Y3, Y2, Y1, Y0} = 4'b0000;

else

case({A0, A1})

2'b00: {Y3, Y2, Y1, Y0} = 4'b0001;

2'b01: {Y3, Y2, Y1, Y0} = 4'b0010;

2'b10: {Y3, Y2, Y1, Y0} = 4'b0100;

2'b11: {Y3, Y2, Y1, Y0} = 4'b1000;

default: {Y3, Y2, Y1, Y0} = 4'b0000;

endcase

endmodule

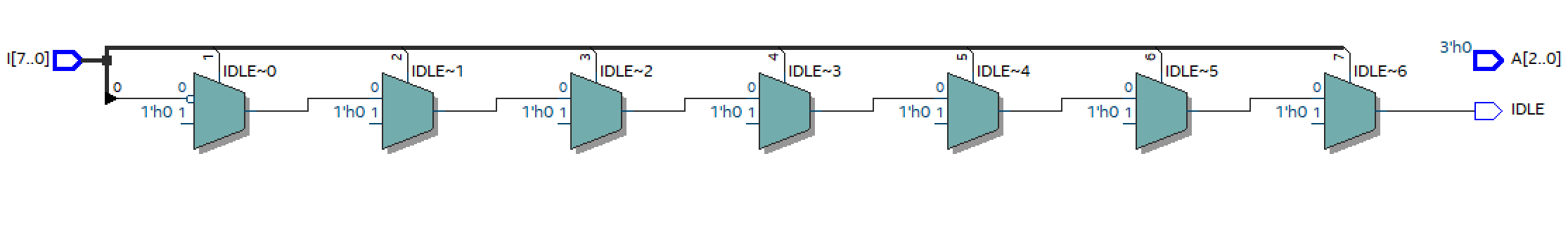

8输入优先编码器

module Vr8inprior(I, A, IDLE);

input [7:0] I;

output reg [2:0] A;

output reg IDLE;

integer j;

always @(*)

begin

IDLE = 1;

A = 0;

for(j = 0; j <= 7; j = j + 1)

if(I[j] == 1)

begin

IDLE = 0;

end

end

endmodule

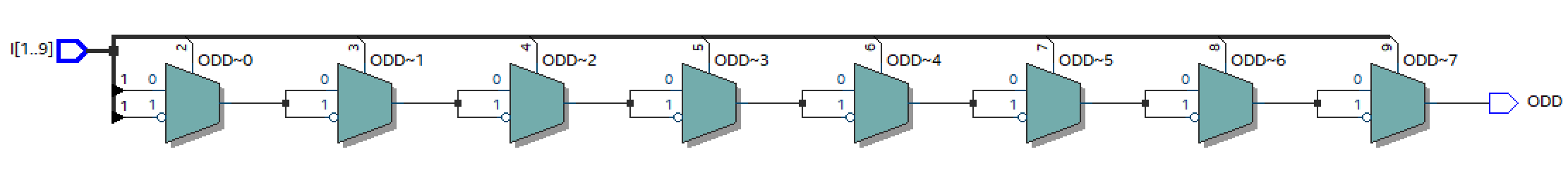

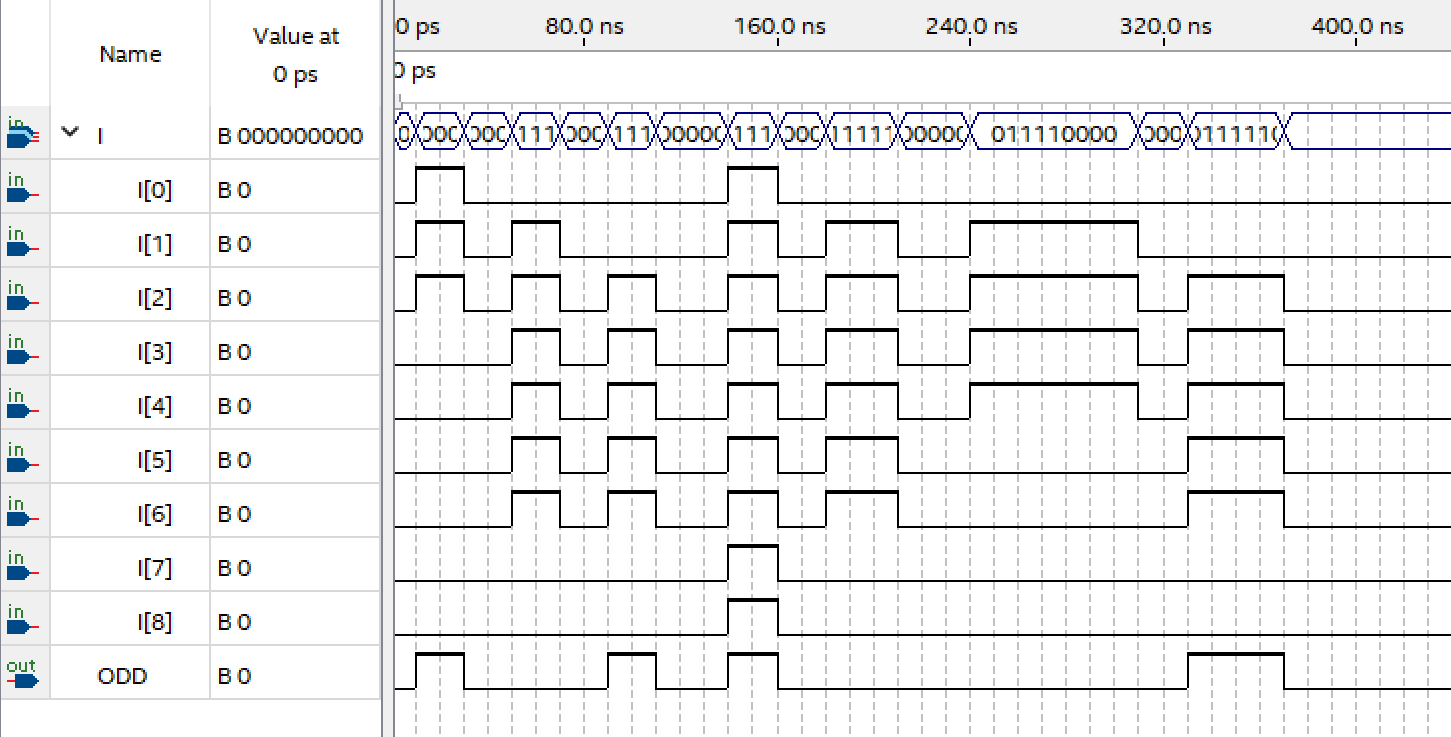

奇偶效验电路

module Vrparity9(I, ODD);

input [1:9] I;

output reg ODD;

integer j;

always @ (*)

begin

ODD = 1'b0;

for(j = 1; j <= 9; j = j + 1)

if (I[j])

ODD = ~ODD;

end

endmodule

八位数值比较器

module Vr8bitcmp(P, Q, PGTQ, PEQQ, PLTQ);

input [7:0] P, Q;

output reg PGTQ, PEQQ, PLTQ;

always @ (*)

if(P == Q)

begin

PGTQ = 1'b0;

PEQQ = 1'b1;

PLTQ = 1'b0;

end

else if(P > Q)

begin

PGTQ = 1'b1;

PEQQ = 1'b0;

PLTQ = 1'b0;

end

else if(P < Q)

begin

PGTQ = 1'b0;

PEQQ = 1'b0;

PLTQ = 1'b1;

end

else

begin

PGTQ = 1'bx;

PEQQ = 1'bx;

PLTQ = 1'bx;

end

endmodule

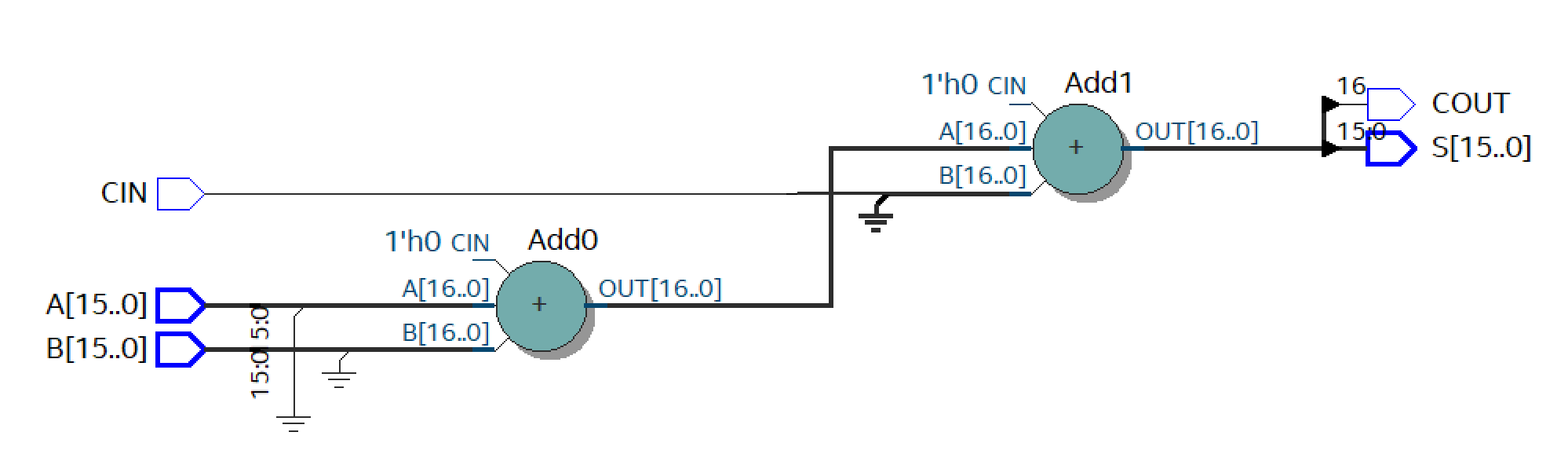

加法器

module VrNbitadder(A, B, CIN, S, COUT);

parameter N = 16; // 加数与和的宽度

input [N-1:0] A, B;

input CIN;

output [N-1:0] S;

output COUT;

assign {COUT, S} = A + B + CIN;

endmodule

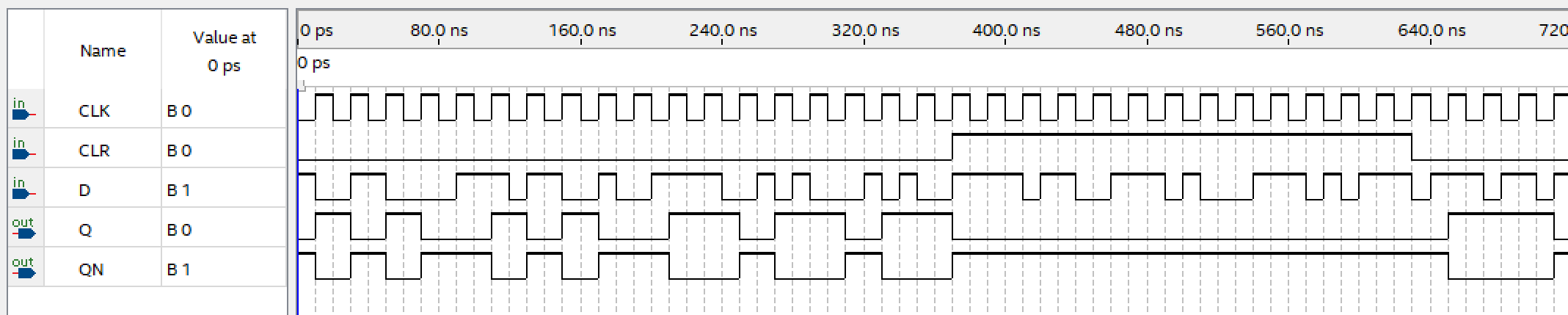

带异步清零和门使能的D锁存器模型

module VrDff(CLK, CLR, D, Q, QN);

input CLK, CLR, D;

output reg Q, QN;

always @ (posedge CLK or posedge CLR)

if (CLR == 1)

begin

Q <= 0;

QN <= 1;

end

else

begin

Q <= D;

QN <= ~Q;

end

endmodule

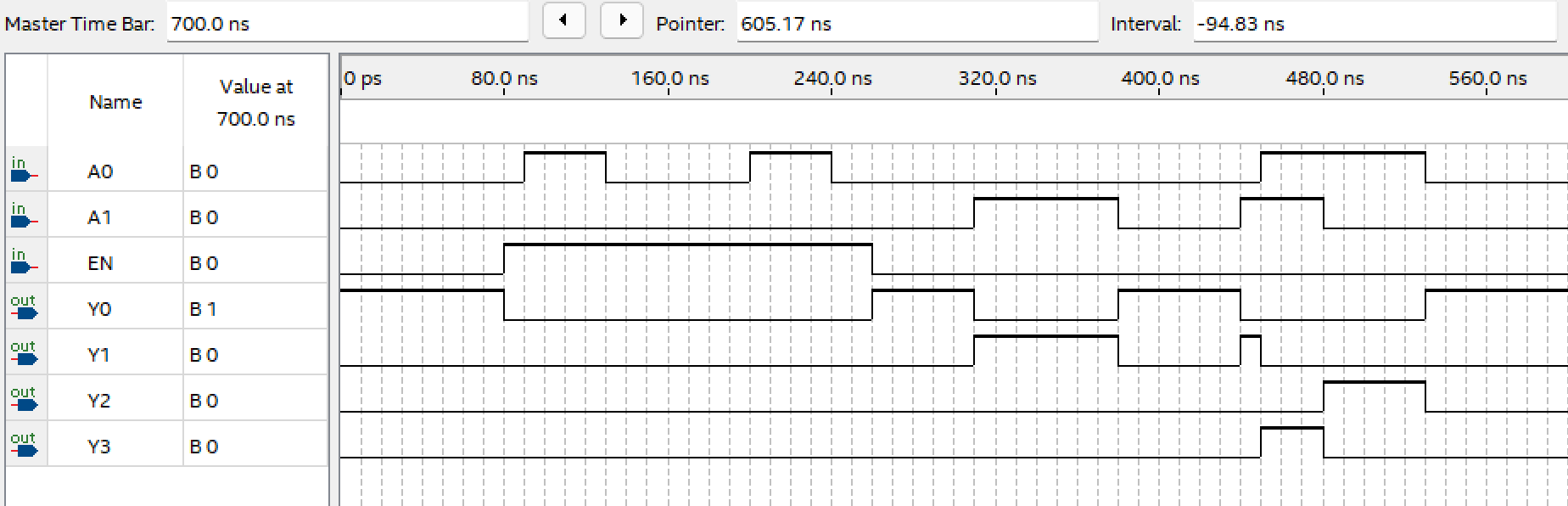

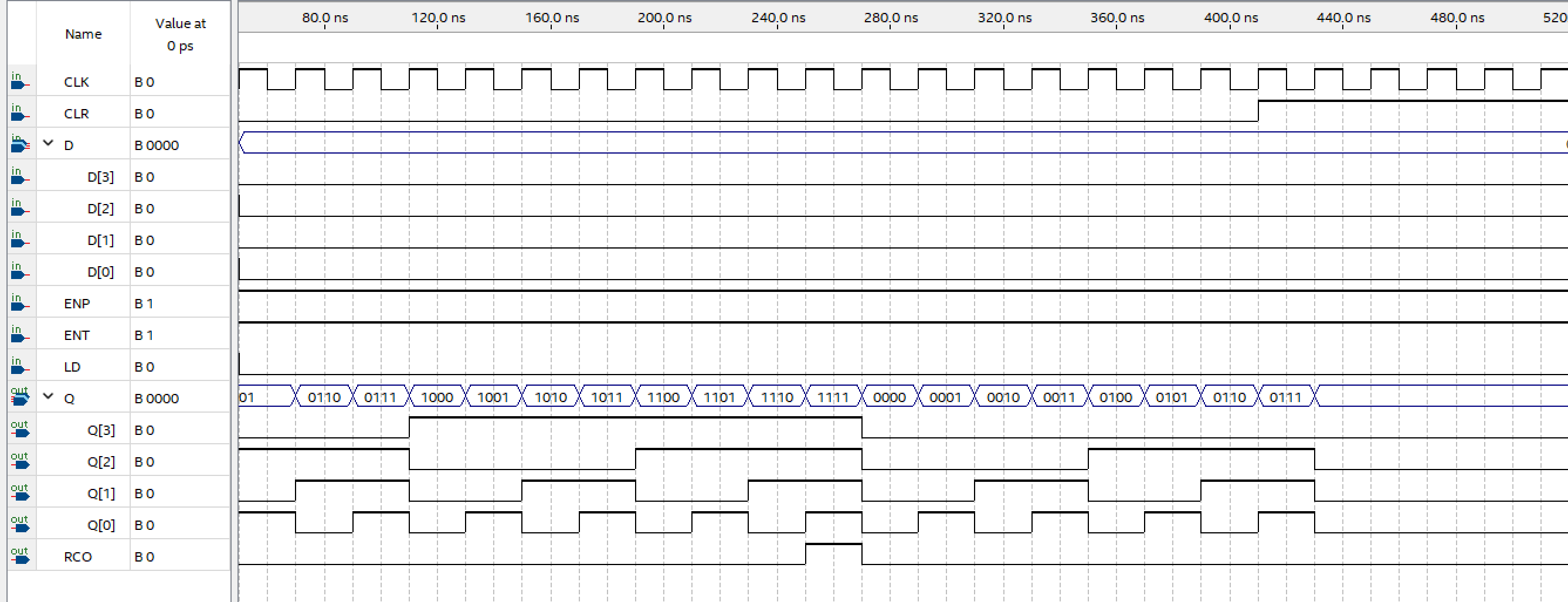

四位二进制计数器

P424

module Vrcntr4u(CLK, CLR, LD, ENP, ENT, D, Q, RCO);

input CLK, CLR, LD, ENP, ENT;

input [3:0] D;

output reg [3:0] Q;

output reg RCO;

always @ (posedge CLK)

if(CLR == 1)

Q <= 4'd0;

else if(LD == 1)

Q <= D;

else if ((ENT == 1) && (ENP == 1))

Q <= Q+1;

else

Q <= Q;

always @ (Q or ENT)

if ((ENT == 1) && (Q == 4'b1111))

RCO = 1;

else

RCO = 0;

endmodule

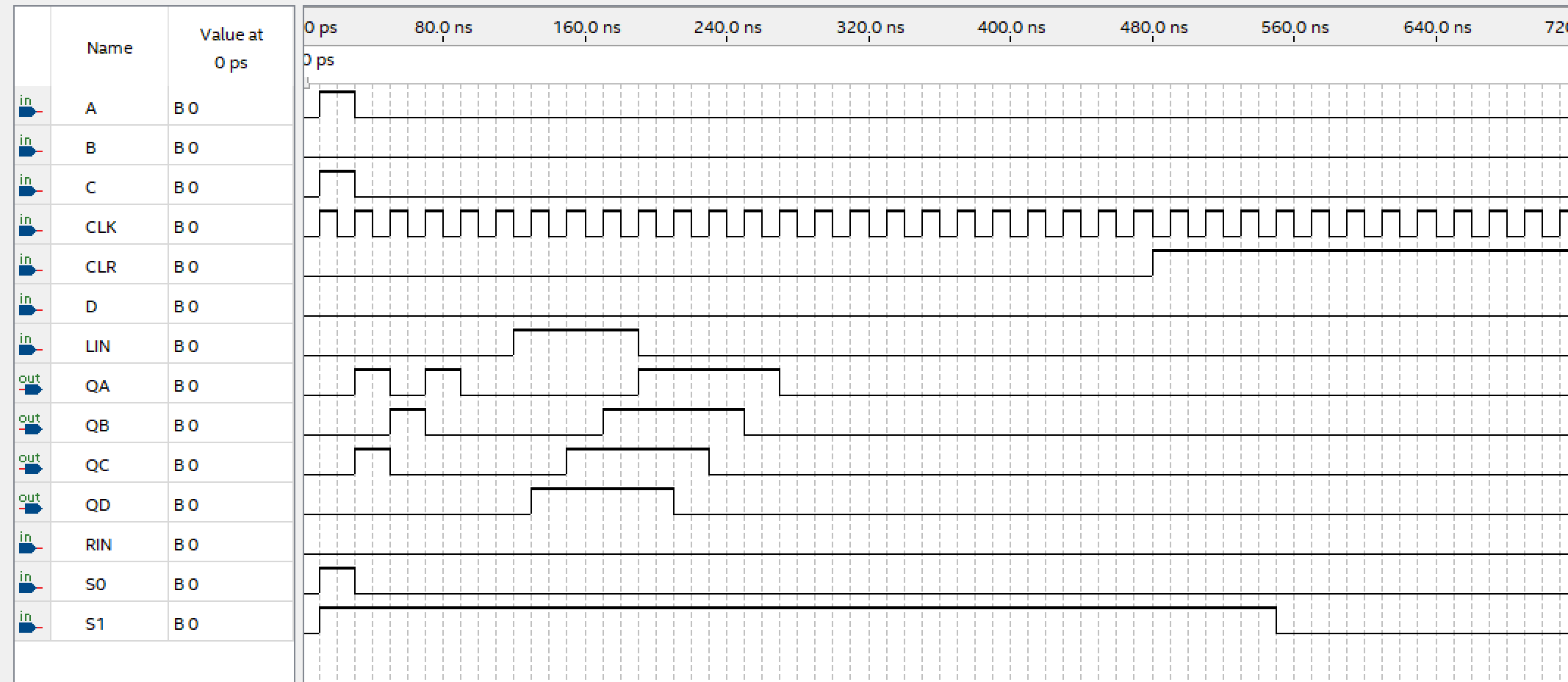

通用四位移位寄存器

P436

module Vrshrg4u(CLK, CLR, RIN, LIN, S0, S1, A, B, C, D, QA, QB, QC, QD);

input CLK, CLR, RIN, LIN, S0, S1, A, B, C, D;

output reg QA, QB, QC, QD;

always @ (posedge CLK)

begin

if (CLR == 1)

{QA, QB, QC, QD} <= 4'b0;

else

case({S1, S0})

2'b00: ; // 保持

2'b01: {QA, QB, QC, QD} <= {RIN, QA, QB, QC}; //右移

2'b10: {QA, QB, QC, QD} <= {QB, QC, QD, LIN}; //左移

2'b11: {QA, QB, QC, QD} <= {A, B, C, D}; //送数

endcase

end

endmodule